爱普生新款RX8901CE即时时钟模组,内建时间戳记功能与应用说明 (上)

爱普生新款RX8901CE即时时钟模组,内建时间戳记功能与应用说明(上)

【RX8901规格功能概述】

Epson RX8901CE是一个RTC模组,具有整合的32.768 kHz数位温度补偿晶体振荡器(Digital Temp. Compensation X'Tal Oscillator )。它包括各种功能,如时间戳记功能,可以在「外部」或「内部事件」发生时记录多达32组日期和时间,以及基本的RTC功能,如时间日历、时间警报、唤醒计时器和时间更新中断。RX8901CE结合了电源自动切换功能,包括防止主电源反向电流的控制电路,维持自动温度校正的精准32.768 kHz振荡器时间源,以及爱普生的低电流消耗技术,在各种系统上实现了更长的电池使用或待机寿命。

【时间戳记相关功能介绍】

RX8901CE支援时间戳记功能,用于记录因EVINn引脚输入讯号变化而产生的外部事件或内部事件(如自监控功能检测到的电压下降或振荡停止状态)而产生的日期/时间和事件因素等资讯。时间戳记功能的主要特点概述如下:

Ÿ 时间戳记触发来源

1. 外部事件侦测输入:

- 最多可支援EVINn ,n=3组通道(EVIN1, EVIN2, EVIN3)

- 内部可设定上拉/下拉电阻

- 信号触发方法可以选择:前缘触发,后缘触发或同时

- 内建杂讯滤波器(可选滤波时间:0 ~ 5000 mS,每一阶为125mS)

- 事件计数器

- 可以监控输入引脚状态

2. 内部状态事件侦测:

- V BAT电压下降侦测

- V DET1电压下降侦测

- V DET2电压下降侦测

- 内部振荡器停止振荡侦测

3. MPU写入触发:

- 写入特定暂存器位址可以触发写入时间戳记

Ÿ 时间戳记缓冲区:

- 256-byte的SRAM

- 支援3种缓冲区操作模式:

FIFO模式:将SRAM用做FIFO记录资料

Direct模式:将SRAM划分为3个区域,用于3组事件通道单独记录资料

SRAM模式:允许读写SRAM

- FIFO模式允许所有类型的事件,最多可记录32组时间戳记资料,以事件触发时间将时间戳记资料以先进先出方法记录于内建SRAM记忆体中。

- Direct模式允许每一组通道最多可记录10组时间戳记资料(通道2可记录12组时间戳记资料)

- 当内建256Bytes SRAM记忆体溢满时,透过OVWEN bit (Over-Write Enable) ,可设定二种写入模式

可自动覆写模式(OVWEN = 1b) :不需确认,允许自动覆写SRAM启始资料区块

未经许可,禁止自动覆写模式(OVWEN = 0b) :未经覆写许可,禁止覆改SRAM

Ÿ 数据纪录:

1/1024秒至1秒、分钟、小时、日、月、年、EVINn的引脚状态、电压下降、振荡状态以及上述时间戳触发因素

Ÿ 即使在备份模式下也可以记录时间戳数据

Ÿ 当外部或内部事件发生时可以产生中断

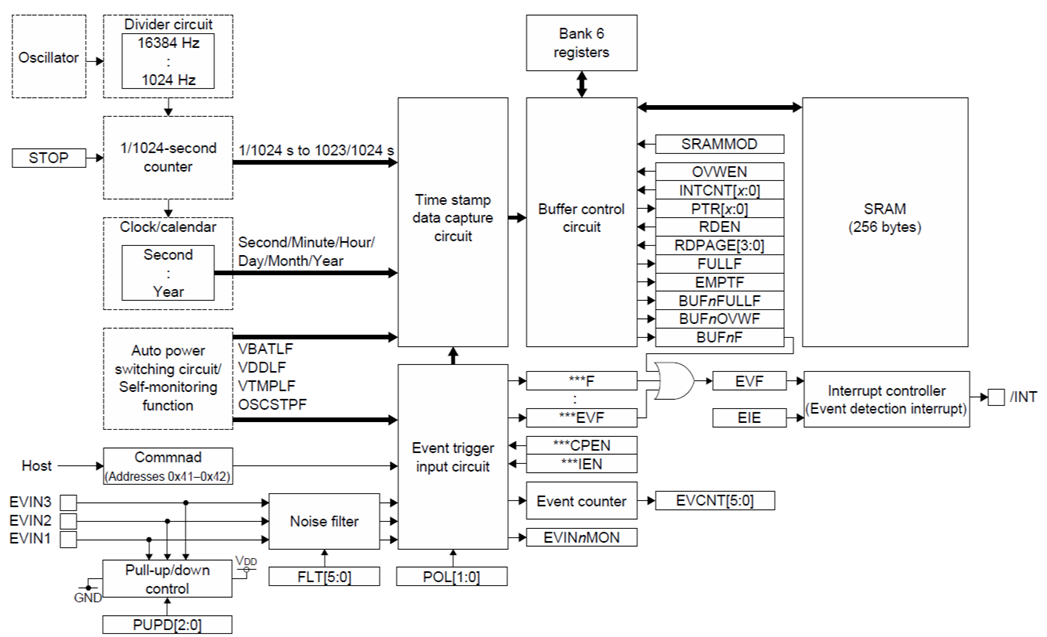

下图一为RX8901CE时间戳记内部电路配置图:

图一: RX8901CE时间戳记内部电路配置图

【RX8901时间戳记触发相关暂存器介绍】

当外部事件、内部事件或写入特定暂存器位址时,RX4901/RX8901在该时间点获取时间戳记资料并写入缓冲区,这些时间戳记触发是指EVINn外部事件侦测输入触发、内部状态侦测触发,与MPU写入触发。

外部事件侦测输入(EVINn引脚)触发

外部事件输入触发讯号从引脚EVIN1 ~ EVIN3 ,下面显示了与外部事件触发输入相关的功能或应设置的条件。

上拉/下拉电阻( PULL Up / Down Resistor )

EVINn引脚可以透过软体写入暂存器设定RX8901内部的上拉/下拉电阻,下表一为EVINn引脚设定上拉/下拉电阻暂存器表:

|

暂存器 EVINn_CFG.PUPD[2:0] |

下拉/上拉电阻值 |

|

0x00 |

无 |

|

0x01 |

上拉500kΩ |

|

0x02 |

上拉1MΩ (预设) |

|

0x03 |

上拉10MΩ |

|

0x04 |

下拉500 kΩ |

|

其他 |

无 |

表一: EVINn引脚设定上拉/下拉电阻暂存器表

杂讯滤波器

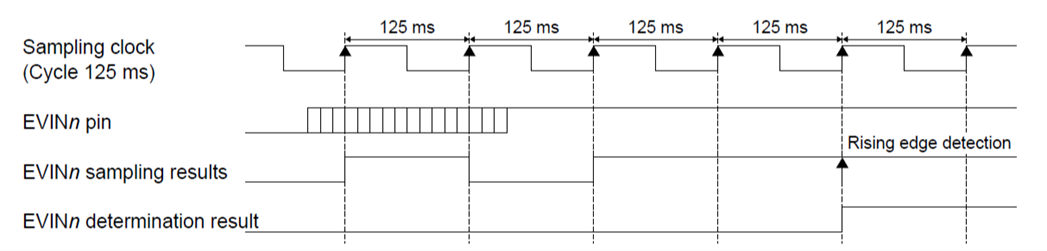

EVINn引脚有一个杂讯滤波器电路,可消除输入讯号上的杂讯。EVINn引脚输入讯号以每125 mS的周期进行采样,当采样结果持续匹配EVINn_FLT.FLT[5:0]位中设置的次数时,即会确定输入采样的逻辑值。

EVINn noise filter: EVINn_FLT.FLT[5:0] bits (Filtering time [ms] = FLT[5:0] × 125)

下表二为EVINn有效输入波形与暂存器EVINn_FLT.FLT[5:0]设定

|

EVINn_FLT.FLT[5:0] |

EVINn波形宽度不确定 (是否侦测到边缘输入讯号取决于边缘输入的时间点和每125mS周期的取样时间) |

有效EVINn波形宽度 (总之侦测到边缘输入讯号) |

|

0x00 |

- |

≧ 1mS |

|

0x01 (禁止设定) |

- |

- |

|

0x02 |

125 mS ~ 250 mS |

≧ 250 mS |

|

0x03 |

250 mS ~ 375 mS |

≧ 375 mS |

|

… |

… |

… |

|

0x27 |

4750 mS ~ 4875 mS |

≧ 4875 mS |

|

0x28 |

4875 mS ~ 5000 mS |

≧ 5000 mS |

|

0x29和之后的数值禁止设定 |

- |

- |

下图二为范例暂存器设定为EVINn_FLT.FLT[5:0] bit = 0x03 ,会在375mS之后开始判断为有效波形:

图二:EVINn杂讯滤波器功能,EVINn_FLT.FLT[5:0] bit = 0x03

备注:

*要确定EVINn引脚输入讯号有效,它必须具有1mS或更多的波形宽度,即使EVINn FLT.FLT|5:0]位设定为0x00 。

*输入讯号在5mS后从输入侦测中获取,因此在获取时间戳记资料之前,会发生5mS的延迟。

前缘、后缘信号触发侦测设定

下表三为设定侦测EVINn输入引脚的边缘讯号

|

EVINn_CFG.POL[1:0] |

侦测边缘讯号 |

|

0x00 |

下降(预设) |

|

0x01 |

上升 |

|

0x02 |

上升或下降 |

|

0x03 |

表三:输入边缘讯号侦测

事件计数器

每组EVINn输入引脚都有一组6-bit计数器,用以计算0~63范围内的输入事件触发,计数器可以从下列暂存器读取:

EVINn事件计数器: EVINn_EVCNT.EVCNT[5:0]

监控器

RX4901CE/RX8901CE提供监控当前EVINn的引脚状态

EVINn监控器: EVINMON.EVINnMON

Command写入触发

WRCMD_CFG.CMDTRGEN设定为1后,可以写入任意值予暂存器WRCMD_TRG即可命令触发时间戳记。

【RX8901时间戳记缓冲区相关暂存器介绍】

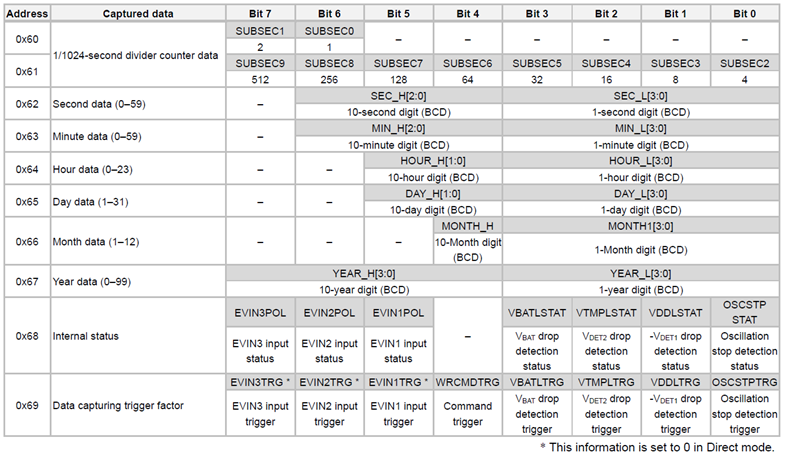

RX4901/RX8901包含了256-byte SRAM用来储存获取的时间戳记资料,在写入实体对应SRAM记忆体区块位置前,时间戳记和事件触发资料,将会先写入如下表四缓冲区资料,可以透过暂存器位址0x60到0x67读取时间戳记,另透过0x68和0x69可读取该笔事件触发讯息。

表四:时间戳记资料与缓冲区读取位址

下个章节会开始介绍缓冲区的工作模式,例如FIFO模式与Direct模式,还有缓冲区相关暂存器、SRAM覆写机制与获取时间戳记的操作等等。