石英晶体振荡器和周边电路设计指南(中)

杂讯消除与抑制对策

序前篇技术文件「杂讯抑制电路设计方法」,我们了解到相关杂讯的来源(石英晶体振荡器内部IC以及其周边电路/电源端与输出讯号端)。

在本篇章节,我们将会进一步探讨与说明,如何降低与抑制杂讯的解决方式。

首先,主要降低杂讯的方式,有以下三种设计参考:

1. 建立稳定的电源与接地设计

2. 抑制电源杂讯的滤波线路设计(安装滤波线路以防止由电源所发出的杂讯)

3. 稳定的输出讯号线配置

在此章节将会先以下列两项参考设计解决方式进行说明;

1. 建立稳定的电源与接地设计

2. 抑制电源杂讯的滤波线路设计

1.稳定的电源和接地设计

稳定的电源和接地设计,是基于在高频的频段会有较低的阻抗,同时为了实现在各频宽下各频率点都能有均匀电位的导通特性考量。而接地线代表电路的基本参考电位,透过更宽阔表面积的接地层设计,以提供最稳定的设计特性。

当在采用多层板设计时,可透过额外的接地层来配置独立的电源线和接地线。

关于焊点设计的部份,采用更宽的接触面积可确保较低的阻抗,进而降低杂讯产生。

2.电源线滤波设计

透过搭配石英晶体振荡器的电路设计为例,通常会在电源端和接地线之间设计一个滤波线路,除了可防止由石英晶体振荡器的杂讯泄漏到电源端或接地线,同时也可避免由电源线向石英晶体振器发出杂讯干扰。

而最为常用的滤波线路设计,大多会是在电源线和接地线之间连接一个或多个旁通电路专用滤波电容器。

a .旁通电路专用滤波电容器

旁通电路上的滤波电容的工作原理,主要是用来降低电阻(抗)间的相互作用,目的在于可以帮助提高整体电路的稳定运作,同时可吸收存在于电源线上的杂讯,这是最为普遍用来降低杂讯的方法。而透过适当的电容器容值设计选用,可以解决大多数与杂讯相关的问题。

i.旁通电路电容器容量选用

标准旁通电路电容值,如果只设计一颗时,建议约保持在0.01μF至1μF间,此旁通电路电容值建议尽可能越小越好。

同时,必须确认此旁通电路电容器电容值的频率特性,以确保在高频或低频段时的阻抗不会增加。

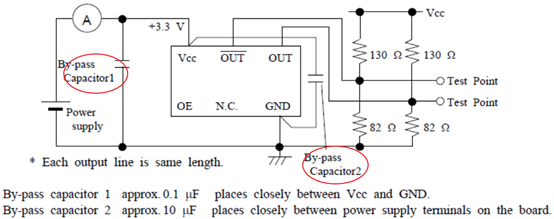

下图参考(高耗电,对电源杂讯极度敏感的「差动式输出」石英晶体振荡器电路设计),当旁通电路滤波用电容采用两颗设计,电容器一容值约0.1μF,建议置放于愈接近Vcc和GND走线间。

电容器二容值约10μF,建议置放于愈接近电路板上电源走线路径上。

采用两颗旁通电路电容器大、小电容量时,可以分别过滤来自电源线上的高频、低频杂讯。

i i.旁通电路电容实装设计

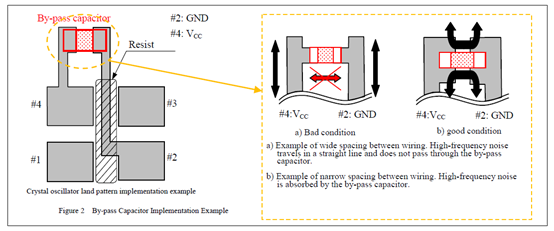

为了降低杂讯干扰,旁通电路用电容应尽可能靠近石英晶体振荡器。因为随着走线长度的增加,寄生电感特性也将随之增加,并导致高频阻抗特性增大,所以必须留意旁通电路电容器的走线设计,以便让信号可经由旁通电路电容器再流通过电源线,这可强制让杂讯通过旁通电路电容器,有效提高杂讯消除。

然而,高频杂讯通常会以直线方式来传递,所以在设计旁通电路电容时,请务必避免使用图2a中的设计方式。如果是使用图2a的设计方式,杂讯将不会通过旁路电容器而无法达到抑制的效果。因此,我们建议采用图2b中显示的图面设计。

本篇为「石英晶体振荡器周边电路的设计参考原则(中) 」,我们将于下期介绍,如何透过优化电路走线方法和设计,降低来自电路杂讯的设计建议,敬请期待。