石英晶体振荡器和周边电路设计指南(全集)

杂讯抑制电路设计方法

[前言]

在电子设备和通信系统的设计与配线过程中,必须审慎考虑石英晶体振荡器和其周边电路相关设计注意事项和原则,方能获得高品质优质振荡信号。作为信号源的核心,使用石英晶体振荡器总是被高度期待能够得到高度精准度信号输出,因此对来自电路板的高频杂讯,总是谨慎以待。该电路在设计过程中需特别注意。以下相关设计注意事项说明,可以降低来自周边电路的杂讯,特别是高频杂讯对石英晶体振荡器输出信号品质引响甚巨。

[几种杂讯来源,来自石英晶体振荡器或其周边电路]

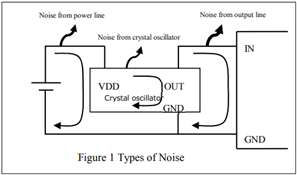

首先,在图1中,我们可概略标示出三种杂讯源,产生自石英晶体振荡器本身或其周边电路。

1. 来自电源线杂讯

2.来自时脉信号输出端杂讯

3.来自石英晶体振荡器自身杂讯

通常所谓的“杂讯” ,主要多是由这三种因素,累积而来。

接着,将说明以上三种类型的杂讯源原因。

1.来自电源线杂讯

通常涟波或是交换式电源供应器所产生的杂讯,常会自电源路径上所发射而出。这种杂讯会影响石英晶体振荡器的输出。此外,也另须确保石英晶体振荡器所产生的涟波杂讯,不会偶合到电源路径上。我们通实采用屏蔽方式来隔离杂讯源,提升石英晶体振荡器输出信号的稳定度。

2.来自时脉信号输出端杂讯

输出端杂讯源泛指因石英晶体振荡器输出信号走线设计不佳,让输出时脉信号走线发生天线效应。时脉信号输出端走线设计时,需考虑防止因设计不当产生天线效应时,所散射出的杂讯。

3.来自石英晶体振荡器控制IC杂讯

石英晶体振荡器控制IC杂讯,是指该振荡器内部IC或线路所产生的杂讯。为消除此杂讯时,需要确保稳定供电电源品质,使其输出波形稳定,让石英晶体振荡器在稳定条件下正常工作运行。这些杂讯源通常来自于上述原因,可以通过接后提到的电源线路和输出线路降低杂讯设计,来提高整体电路和信号品质,并且降低杂讯。

上述的杂讯散射强度,和其通过电流大小和电流流经路径成正比。因此,随着电流量或电流流经路径的阻抗降低时,相关杂讯散射强度亦会同时降低。一般来说,电流和电流流经路径的长度,存在着以下关连性,因为它与石英晶体振荡器及其周边电路有关。

电流流量:电源线=石英晶体振荡器>时脉信号输出走线

电流路径大小:时脉信号输出>电源线>>石英晶体振荡器

时脉信号输出走线所产生的杂讯,对石英晶体振荡电路的影响最大,其次是来自电源端的杂讯。相较于以上两种杂讯源影响,来自石英晶体振荡器内部IC的杂讯,影响甚小。

[杂讯消除与抑制对策]

首先,主要降低杂讯的方式,有以下三种设计参考:

1.建立稳定的电源与接地设计

2.抑制电源杂讯的滤波线路设计(安装滤波线路以防止由电源所发出的杂讯)

3.稳定的输出讯号线配置

1.稳定的电源和接地设计

稳定的电源和接地设计,是基于在高频的频段会有较低的阻抗,同时为了实现在各频宽下各频率点都能有均匀电位的导通特性考量。而接地线代表电路的基本参考电位,透过更宽阔表面积的接地层设计,以提供最稳定的设计特性。

当在采用多层板设计时,可透过额外的接地层来配置独立的电源线和接地线。

关于焊点设计的部份,采用更宽的接触面积可确保较低的阻抗,进而降低杂讯产生。

2.电源线滤波设计

透过搭配石英晶体振荡器的电路设计为例,通常会在电源端和接地线之间设计一个滤波线路,除了可防止由石英晶体振荡器的杂讯泄漏到电源端或接地线,同时也可避免由电源线向石英晶体振器发出杂讯干扰。

而最为常用的滤波线路设计,大多会是在电源线和接地线之间连接一个或多个旁通电路专用滤波电容器。

a .旁通电路专用滤波电容器

旁通电路上的滤波电容的工作原理,主要是用来降低电阻(抗)间的相互作用,目的在于可以帮助提高整体电路的稳定运作,同时可吸收存在于电源线上的杂讯,这是最为普遍用来降低杂讯的方法。而透过适当的电容器容值设计选用,可以解决大多数与杂讯相关的问题。

i.旁通电路电容器容量选用

标准旁通电路电容值,如果只设计一颗时,建议约保持在0.01μF至1μF间,此旁通电路电容值建议尽可能越小越好。

同时,必须确认此旁通电路电容器电容值的频率特性,以确保在高频或低频段时的阻抗不会增加。

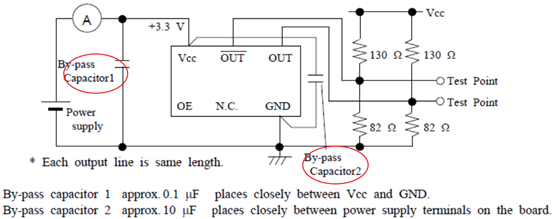

下图参考(高耗电,对电源杂讯极度敏感的「差动式输出」石英晶体振荡器电路设计) ,当旁通电路滤波用电容采用两颗设计,电容器一容值约0.1μF ,建议置放于愈接近Vcc和GND走线间。

电容器二容值约10μF ,建议置放于愈接近电路板上电源走线路径上。

采用两颗旁通电路电容器大、小电容量时,分别过滤来自电源线上的高频、低频杂讯。

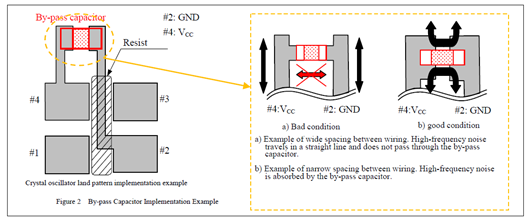

i i.旁通电路电容实装设计

为了降低杂讯干扰,旁通电路用电容应尽可能靠近石英晶体振荡器。因为随着走线长度的增加,寄生电感特性也将随之增加,并导致高频阻抗特性增大,所以必须留意旁通电路电容器的走线设计,以便让信号可经由旁通电路电容器再流通过电源线,这可强制让杂讯通过旁通电路电容器,有效提高杂讯消除。

然而,高频杂讯通常会以直线方式来传递,所以在设计旁通电路电容时,请务必避免使用图2a中的设计方式。如果是使用图2a的设计方式,杂讯将不会通过旁路电容器而无法达到抑制的效果。因此,我们建议采用图2b中显示的图面设计。

3.稳定的输出讯号线配置

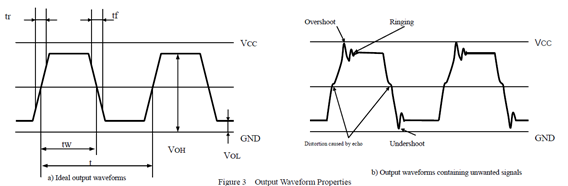

稳定的输出讯号线配置,是指能在最小的讯号失真以及电磁辐射的影响下,有效透过输出讯号线的配置设计,将石英晶体振荡器的输出讯号(波形)传输到下一级元件的输入端。而为了确保能提供符合输入端的波形特性要求(如tr 、tf 、VOH 、VOL等) ,该如何设计稳定的输出讯号线就变的非常重要。此外,稳定的输出线路设计也需要能够消除不需要的信号,例如Overshoot 、Undershoot 、Ring和Echo ,如Figure 3b所示。

同时,为了能降低不必要的讯号干扰,走线时可能发生的天线效应,也必须特别留意。

一般而言,防止输出波形失真的方式,有以下四种方式:

a.配接串联电阻

b.配接终端电阻

c.配置滤波线路

d.输出线路阻抗匹配

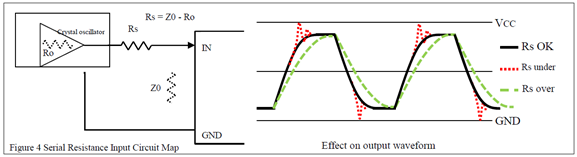

a.配接串联电阻

将石英振荡器连接到输入元件时通常会导致波形失真,包括Overshoot 、Undershoot和Ringing 。这些失真主要是因为接收到未被消除的高频杂讯,而这种高频杂讯,大多比振荡频

率高出3-7倍。为了消除这种失真,石英振荡器的输出端和下一级元件的输入端之间需连接串联电阻,如下Figure 4所示。

输出线路阻抗(Z0)是由石英振荡器的输出阻抗(Ro)和串联电阻(Rs)的加总而成。串联电阻(Rs)的最佳值,可以透过实际测试的方式来确认,而测试的方法可以将串联电阻(Rs)从较低的电阻值转换为高阻值,并使用示波器量测输出波形,当该电阻值能够有效消除Overshoot 、Undershoot和Ringing ,即为最佳电阻值。

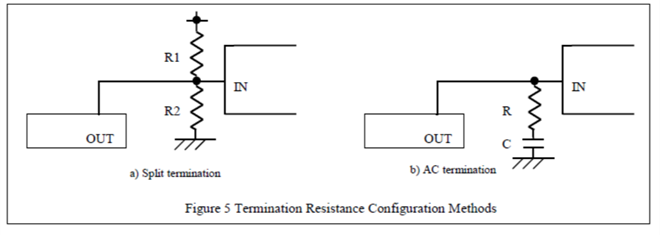

b.配接终端电阻(Termination Resistance)

终端电阻的配置,主要是取决于介面类型和所用时脉讯号线的类型。

当输出线路的阻抗与元件输入的阻抗不匹配时,输出波形将会出现失真,无法接收到完整的讯号,部分讯号将会被反射回石英振荡器,导致输出波形失真以及高频杂讯。如果将石英振荡器输出讯号分支到多个元件时,这种波形失真将会导致错误触发讯号的产生。因此,如何选用正确的终端电阻(Termination resistance)以及阻抗匹配就变的非常重要。

为了防止来自接收设备的Echo ,输入讯号端与输出讯号端的线路阻抗值必须相同。

Figure 5显示了两种常见的连接方法:分路端接和交流端接。

c.滤波器设定

通常,输出波形失真可以使用串联电阻或连接终端电阻(Termination resistance)来解决。但是如果这些方法仍无法解决波形失真的问题时,就会采用滤波器设计的方式来解决。使用滤波器是消除高频杂讯的有效方法,但这种方法会导致tr和tf的增加。因此,必须选择相容于tr和tf特性的滤波器。

此外,如使用较大的电容器作为滤波器的使用则会导致电流增加,从而相反导致杂讯增加。

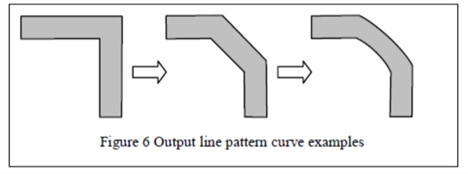

d.输出线路阻抗匹配

为了能减少输出线路上的波形Echo(回波) ,尽可能要求输出线路阻抗能够一致。为能实现一致的输出线阻抗,输出线的走线设计也是重要的关键之一,如Figure 6所示,可由直角转换为45°角,或者可能的话,也可采用圆角曲线的设计以提高输出线路阻抗的一致性。此外,应避免使用穿孔设计或T型分支设计。

最后,为有效降低杂讯发射的影响,我们总结两种最重要的方法来进行说明。

a.使用较短的输出线

在所有电路设计应用中,输出讯号线是最容易产生杂讯。因此,在线路设计布线(Layout)的过程中,应优先考虑使用最短的输出线路,以将阻抗变动的影响降到最小。而使用较短的布线(Layout)会将输出线谐振频率转移到高频侧,当频率越高时,在频率输出元件所发生的阻尼就越多,这样的设计方式可以降低杂讯发射。

b. 使用较短的电流回路路径

一般来说,由输出线路发出的杂讯等级会与电流回路的路径长度成正比。

因此,从石英振荡器输出端到下一级元件的输入端与接地的走线长度必须尽可能越短越好。而为了实现这个目标,最简单方法则是将接地层安装在输出端走线的另一侧。

除了经由上述所说明的方法来降低杂讯的影响之外,透过石英振荡器及其周边电路的优化设计则变的非常重要。最佳化电路设计除了可以避免与杂讯相关的问题发生,同时也可以使相关电子元件能够充分发挥其最佳效能。

以上为日本精工爱普生针对石英振荡器或振荡电路相关设计杂讯消除与抑制对策经验分享,如有任何设计问题时,可洽询台湾爱普生公司各授权电子零件代理商,或是与我们联络。

原文来自: https://www5.epsondevice.com/en/information/technical_info/pdf/tech_notes_circuit_design20140624.pdf

更多精工爱普生技术撰文: https://www5.epsondevice.com/en/information/technical_info/white_paper.html